## 平成 11 年度開始未来開拓学術研究推進事業研究プロジェクト 「超集積化デバイス・システム第 165 委員会」産学協力研究委員会

Research and Development of code-division-multiple-access data bus and its application for intelligent information systems

# CDMA データバスとそれを用いた 高度情報処理システムの研究開発

プロジェクトリーダー 谷 口 研 二 大阪大学 大学院工学研究科 教授

### 1. 研究の目的

集積回路技術は今日の高度情報化社会を支える技術の1つですが、種々の機能を有する回路を1つのシリコンチップに集積したシステムLSIも実現する時代になってきています。しかし、設計されるシステムLSIの規模が大きくなり、情報処理の複雑さが増すと、チップの内外での配線数が必然的に増加し、(1)製造プロセス工程の増加によるチップコストの高沸、(2)製造プロセスでの歩留まりの低下、(3)配線駆動電力の増大、などの問題が表面化します。

このプロジェクトでは、このような将来のLSIが抱える問題を事前に解決することを目指しています。その目的は、(1)上記の諸問題を解決する革新的なデータ転送インターフェース技術を開発すること、(2)このインターフェース技術の特長を生かすLSIシステムを実現し、新技術の有効性を実証すること、(3)新しい高度情報処理システム構築の基盤を固めること、です。具体的には、携帯電話などに応用されている「符号分割多重データ通信(CDMA)」という技術をLSIチップ間のデータ転送に利用し、特定のチップから不特定多数チップへの一括データ転送、

任意のチップ間の相互多重データ通信、などを少数のバスラインで実現するための基盤技術を研究開発します。

本研究により、符号分割多重データ転送方式の長所(自由な通信配線トポロジーが可能、配線数を大幅に低減することが可能)を生かして、超並列プロセッサシステム、ニューロ(神経回路網)システムなどに応用されると期待されます。

### 2. 研究の内容

現在のLSIでは、多数のバスライン上をデジタル信号が伝達しています。しかし、このままでは、情報処理が複雑になると、配線が複雑になったり、ピン数が増大する一方です。また、それとともに、消費電力の増大を抑えることが困難になってきます。もしも、1本のバスラインで多数の信号を同時に転送することが可能となれば、このような問題に対する1つのブレークスルーとなります。この研究プロジェクトでは、携帯電話などに応用されている「符号分割多重データ通信(CDMA)」という技術を用いて、少数の有線バスラインもしくは無線通信で多数の信号を転送するためのインターフェース回路の研究開発を推し進めています。

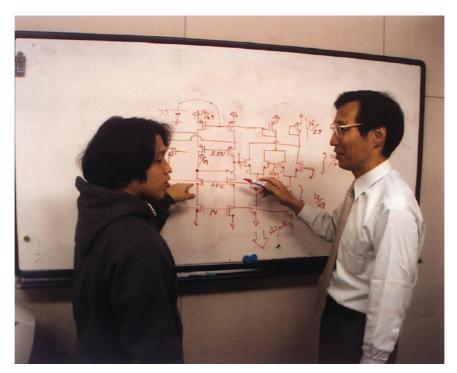

#### (1)符号分割有線データバス・インターフェース回路

有線バスラインでは、ベースバンドで符号分割多重方式を用いています。この方式では、擬似ノイズというランダムなコード用いています。異なる擬似ノイズを各々の送信データに乗算し、データバス上に多重化します。データバスには、ステップ状のアナログ信号が伝達されます。受信側では、この信号に所望の送信データに対応する擬似ノイズを乗算して、不要な高周波成分を除去することにより、必要な信号を受信することができます。このデータバスのアナログ信号のノイズに対する耐性を確保するため、差動バスラインを用いて検討しています。現在、送信及び受信のインターフェース回路の研究開発を精力的に推し進めています。

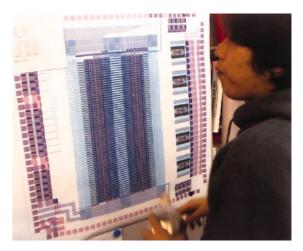

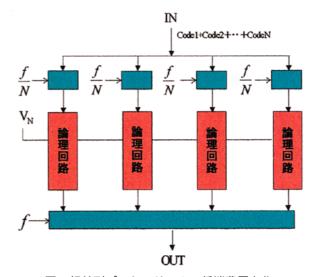

また、このインターフェース回路を用いて超並列プロセッサーを構成すると、配線トポロジーが簡単になります。現在のCPUのようにクロック周波数を上げなくても、この超並列プロセッサでは高度な情報処理ができるので、システム全体の低消費電力化が可能になります。さらに、このインターフェース回路ではLSI内部の各ブロック間の通信トポロジーを動的に変えることができます。現在、このような特長を生かした新しい演算処理回路についても研究開発しています。

#### (2) 高周波無線通信チップ間インターフェース回路

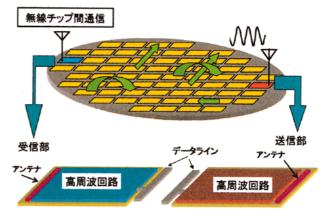

十年後にはLSIチップ内で使用するクロック周波数は数GHzにも達します。このようなチップでは、数cmの金属配線はアンテナとして働き、チップ内の信号は外部に自然放出されます。このプロジェクトでは、この自然電波放出を逆手にとって通信手段に利用するため、現在、高周波無線技術と符号分割多重方式を用いて、同一周波数帯域で多数の信号を伝送するためのインターフェース回路を研究開発しています。これをLSIチップ間のデータ転送に用いることで、ピン数を大幅に削減することが可能となります。さらに、無線データ通信を介したLSIチップの三次元的な実装も容易になり、大規模システムの小型実装の実現が期待されます。

#### 3. 研究の体制

期 間:1999年8月~2004年3月 構 成:プロジェクトリーダー1名

コアメンバー3名

研究協力者2名(内ポスドク1名) 実施場所:大阪大学工学部 吹田市山田丘2-1 図1有線チップ間通信の概念図

図2超並列プロセッサによる低消費電力化

図3無線チップ間通信の概念図