# 先端研究助成基金助成金(最先端・次世代研究開発支援プログラム) 実績報告書

本様式の内容は一般に公表されます

| 研究課題名          | ナノ半導体におけるキャリア輸送・熱輸送の統合理解によるグリーンLSIチップの創製 |  |

|----------------|------------------------------------------|--|

| 研究機関·<br>部局·職名 | 慶應義塾大学・理工学部・教授                           |  |

| 氏名             | 内田 建                                     |  |

1. 研究実施期間 平成23年2月10日~平成26年3月31日

## 2. 収支の状況

(単位:円)

|      | 交付決定額       | 交付を受け<br>た額 | 利息等収入<br>額 | 収入額合計       | 執行額         | 未執行額 | 既返還額 |

|------|-------------|-------------|------------|-------------|-------------|------|------|

| 直接経費 | 132,000,000 | 132,000,000 | 6,697      | 132,006,697 | 132,006,697 | 0    | 0    |

| 間接経費 | 39,600,000  | 39,600,000  | 0          | 39,600,000  | 39,600,000  | 0    | 0    |

| 合計   | 171,600,000 | 171,600,000 | 6,697      | 171,606,697 | 171,606,697 | 0    | 0    |

## 3. 執行額内訳

(単位:円)

|   |         |           |            |            |            | (早世:口)      |

|---|---------|-----------|------------|------------|------------|-------------|

| 費 | 間       | 平成22年度    | 平成23年度     | 平成24年度     | 平成25年度     | 合計          |

|   | 物品費     | 5,171,000 | 60,449,924 | 29,567,839 | 13,615,723 | 108,804,486 |

|   | 旅費      | 0         | 1,547,018  | 1,960,830  | 1,099,126  | 4,606,974   |

|   | 謝金・人件費等 | 0         | 772,861    | 205,174    | 556,904    | 1,534,939   |

|   | その他     | 0         | 6,027,307  | 8,434,498  | 2,598,493  | 17,060,298  |

| 直 | 接経費計    | 5,171,000 | 68,797,110 | 40,168,341 | 17,870,246 | 132,006,697 |

| 間 | ]接経費計   | 1,551,300 | 20,639,133 | 12,321,567 | 5,088,000  | 39,600,000  |

| 슫 | 計       | 6,722,300 | 89,436,243 | 52,489,908 | 22,958,246 | 171,606,697 |

### 4. 主な購入物品(1品又は1組若しくは1式の価格が50万円以上のもの)

| 物品名                 | 仕様・型・性<br>能等                                                | 数量 | 単価<br>(単位:円) | 金額<br>(単位:円) | 納入<br>年月日 | 設置研究機関名                 |

|---------------------|-------------------------------------------------------------|----|--------------|--------------|-----------|-------------------------|

| 2位相DSPロックインアンプ      | 7280                                                        | 1  | 2,217,600    | 2,217,600    | 2011/3/11 | 慶應義塾大学(東京工業大学より移管)      |

| 自動キャパシタンスブリッジ       | AH2550A                                                     | 1  | 2,952,600    | 2,952,600    | 2011/3/30 | 慶應義塾大学(東京工業大<br>学より移管)  |

| 精密インピーダンス アナライ<br>ザ | 米国アジレン<br>ト・テクノロ<br>ジー社製<br>4294A・42941<br>A・16048H         | 1  | 5,217,555    | 5,217,555    | 2011/5/27 | 慶應義塾大学(東京工業大<br>学より移管)  |

| ハイパフォーマンスコンピュー<br>タ | HPCシステム<br>ズ(株)製・<br>HPC5000-<br>Z800-SIP外                  | 1  | 2,174,487    | 2,174,487    | 2011/6/7  | <br> 慶應義塾大学(東京工業大学より移管) |

| 膜厚モニター一式            | インフィコン<br>(株)製・SQM-<br>160(真空蒸<br>着装置<br>SVC-700用)<br>オリンパス | 1  | 1,059,439    | 1,059,439    | 2011/6/27 | 慶應義塾大学(東京工業大学より移管)      |

| 半導体検査顕微鏡            | オリンパス<br>(株)製・<br>MX61-<br>N873MD,U-<br>ECA,DP21-           | 1  | 2,501,100    | 2,501,100    | 2011/6/20 | 慶應義塾大学(東京工業大学より移管)      |

| BA4850 高速バイポーラ電源    | BA4850                                                      | 1  | 648,375      | 648,375      | 2011/7/8  | 慶應義塾大学(東京工業大学より移管)      |

### 様式20

|                              | 720 2.1 =                                           |   |            |            |            |                        |

|------------------------------|-----------------------------------------------------|---|------------|------------|------------|------------------------|

| 高速パルス電圧駆動型電気特<br>性評価システム     | アジレント・テ<br>クノロジー社<br>製・<br>B1500A/B15<br>17A/B1530A | 1 | 16,927,575 | 16,927,575 | 2011/10/7  | 慶應義塾大学(東京工業大学より移管)     |

| 高真空低温プローバー                   | 米国レイク<br>ショア社製・C<br>PXーHVS<br>アジレント・テ               | 1 | 15,996,750 | 15,996,750 | 2011/12/21 | 慶應義塾大学(東京工業大<br>学より移管) |

| 低リークスイッチ                     | クノロジー社<br>製・B2201A<br>(中古品)                         | 1 | 2,625,000  | 2,625,000  | 2011/12/13 | 慶應義塾大学(東京工業大学より移管)     |

| 半導体パラメータアナライザ                | 米国アジレント・テクノロ<br>ジー社製・<br>4156C S/N<br>JP10J01670    | 1 | 2,310,000  | 2,310,000  | 2012/2/15  | 慶應義塾大学(東京工業大学より移管)     |

| 液体ヘリウム容器/トランス<br>ファーライン挿入ヘッド | クライオーサ<br>ム社製・<br>STRATOS10<br>OSL                  | 1 | 1,478,400  | 1,478,400  | 2012/2/20  | 慶應義塾大学(東京工業大<br>学より移管) |

| デルタモードシステム                   | ケースレーイ<br>ンスツルメン<br>ツ<br>6221/2182A/                | 1 | 997,500    | 997,500    | 2012/2/10  | 慶應義塾大学(東京工業大<br>学より移管) |

| テ゛ュアルチャネルフ゜ロク゛ラマフ゛ルフィルタ      | 3628                                                | 1 | 960,750    | 960,750    | 2012/7/23  | 慶應義塾大学                 |

| 低リークスイッチメインフレーム              | E5250A                                              | 1 | 542,745    | 542,745    | 2012/11/6  | 慶應義塾大学                 |

| 電子ビーム式真空蒸着装置                 | SVC-<br>700LEB/4G                                   | 1 | 13,993,665 | 13,993,665 | 2013/2/8   | 慶應義塾大学                 |

| ドラフトチャンバー                    | S.V-120TN                                           | 1 | 2,992,500  | 2,992,500  | 2012/12/27 | 慶應義塾大学                 |

| 超音波熱圧着ウエッジワイヤーホルター           | 7476D                                               | 1 | 2,940,000  | 2,940,000  | 2012/12/20 | 慶應義塾大学                 |

| 乾式ドラフトチャンバー                  | 特型                                                  | 1 | 1,690,500  | 1,690,500  | 2013/2/27  | 慶應義塾大学                 |

| コンハ゜クトエッチャー                  | FA-1                                                | 1 | 4,599,000  | 4,599,000  |            | 慶應義塾大学                 |

| ガス供給設備装置                     | 型番なし                                                | 1 | 2,698,500  | 2,698,500  |            | 慶應義塾大学                 |

| 液体窒素デュワー                     | PS-LN2/J                                            | 1 | 604,800    | 604,800    |            | 慶應義塾大学                 |

| 8チャンネルメインフレーム                | MS-523型                                             | 1 | 585,480    | 585,480    | 2013/12/25 | 慶應義塾大学                 |

## 5. 研究成果の概要

本課題では、ナノ半導体における電荷・熱の輸送を統合的に理解することで、電子デバイスの消費電力を低減しようという新しい試みの基礎研究を行った。近年、立体構造あるいは絶縁膜上に作製したトランジスタが注目されている。これらの熱解析を実験・理論の両面から行い、デバイス局所温度測定方法の開発、絶縁膜ー半導体界面で電子エネルギーが熱に容易に変換されることの発見、温度上昇は生じないとされていた構造でも有意な温度上昇が生じることの実証、デバイス発熱抑制手法の提案、などで世界的な注目を集めた。これらの研究成果は、低エネルギー・高信頼性のLSIの実現を可能とし、グリーンイノベーションの推進に役立つと期待できる。

課題番号 GR034

# 先端研究助成基金助成金(最先端・次世代研究開発支援プログラム) 研究成果報告書

本様式の内容は一般に公表されます

| 研究課題名       | ナノ半導体におけるキャリア輸送・熱輸送の統合理解によるグリーンLSI<br>チップの創製                                                                                  |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| (下段英語表記)    | Unified Understanding of Carrier and Thermal Transports in Nanoscale<br>Semiconductors for the Realization of Green LSI Chips |  |  |  |  |  |

| 研究機関・部局・    | 慶應義塾大学・理工学部・教授                                                                                                                |  |  |  |  |  |

| 職名 (下段英語表記) | Faculty of Science and Technology, Keio University                                                                            |  |  |  |  |  |

| 氏名          | 内田 建                                                                                                                          |  |  |  |  |  |

| (下段英語表記)    | Ken Uchida                                                                                                                    |  |  |  |  |  |

### 研究成果の概要

(和文): 本課題では、ナノ半導体における電荷・熱の輸送を統合的に理解することで、電子デバイスの消費電力を低減しようという新しい試みの基礎研究を行った. 近年、立体構造あるいは絶縁膜上に作製したトランジスタが注目されている. これらの熱解析を実験・理論の両面から行った. デバイス温度測定法の開発、絶縁膜ー半導体界面で電子エネルギーが熱により容易に変換されることの発見、温度上昇が生じ難いとされていた構造でも有意な温度上昇が生じることの実証、デバイス発熱抑制手法の提案、などで世界的な注目を集めた. これらの研究成果は低エネルギー・高信頼のLSIの実現を可能としグリーン・イノベーションの推進に役立つと期待できる.

(英文): The objectives of this project are 1) to achieve unified understanding of carrier and thermal transports in nanoscale electronic devices and 2) to reduce the energy consumption of electronic devices in large-scale integrated circuits (LSIs) by utilizing the above mentioned unified understanding. Recently, three-dimensional electronic devices or devices fabricated on electronic insulating materials have attracted great interests. We fabricated these devices, measured their characteristics, and analyzed the obtained data. As a result, we 1) developed a new method to measure the temperature of nano devices, 2) found that the electron energy is converted to lattice energy more easily at the semiconductor-insulator interface than in bulk, and 3) confirmed that the channel temperature is increased because of self-heating even in nano devices where the local temperature has been considered not to be increased. These results will lead to the realization of low-energy and high-reliability LSI, and thereby contribute to the green innovation.

- 1. 執行金額 171,606,697円 (うち、直接経費 132,006,697円、間接経費 39,600,000円)

- 2. 研究実施期間 平成23年2月10日~平成26年3月31日

#### 3. 研究目的

ナノ半導体(特徴的なサイズが 10 nm 以下の半導体)は次世代エレクトロニクスの基盤材料として注目されている。半導体がナノスケールにまで小さくなると、量子効果などによりバルク結晶とは異なる性質を持ち、新しい機能を持った電子デバイスの実現が期待される。ところが従来、このような新機能の検証は、外場が極めて小さな平衡状態を仮定することでなされてきた。一方で、ナノ半導体を使いこなしていくためには、ナノ半導体内での電界が大きな、非平衡状態におけるキャリア輸送と発熱現象を理解すること、また発生した熱の輸送現象を理解することが不可欠である。

本課題では、以下の 4 項目を目標として掲げた。すなわち、(1)ナノ半導体デバイスの熱的特性の評価、(2)ナノ半導体におけるフォノン特性の特異性の検証、(3)電界が高い場合のナノ半導体におけるキャリア輸送特性の基礎学理の確立、(4)これらを統合的に理解することで、ナノ半導体を用いた高性能・超低消費電力の大規模集積回路(グリーンチップ)を創製するための設計指針の構築、の 4 項目を目標とした。

#### 4. 研究計画·方法

本課題は研究代表者が主宰する研究室において実施し、研究室の全メンバーがデバイス作製、作製したデバイスの特性評価、データの解析、物理モデルの検討、数値計算(シミュレーション)によるモデルの検証を担当した。また、独立行政法人産業技術総合研究所ナノエレクトロニクス研究部門と共同で、つくばイノベーションアリーナ推進本部の支援を受け、ゲート長が 40 nm 程度の微細トランジスタを作製した。集積回路への応用検討では黒田忠広(慶應義塾大学)、ナノデバイスの熱特性評価では柳田剛(阪大産研)、デバイスシミュレーションでは渡辺浩志(台湾国立交通大学)と共同研究を進めた。

目標とした4項目については、以下の計画・方法により達成することを目指した。

(1)ナノ半導体デバイスの熱的特性の評価では、ナノ半導体デバイスの作製が最も難しくかつ重要である。ナノ構造の作製には、文部科学省「ナノテクノロジープラットフォーム」事業「微細加エナノプラットフォームコンソーシアム」の実施機関である東京工業大学の電子線描画装置を活用した。また、独立行政法人産業技術総合研究所ナノエレクトロニクス研究部門とつくばイノベーションアリーナ推進本部と共同でゲート長が 40 nm 程度の微細トランジスタを作製した。動作時のデバイスの温度特性評価では、ポリシリコン細線や金属細線によるナノ温度計を利用した。最終的には、ナノ温度計に適した材料を選択したが、開発途上においても材料に応じた温度の補正方法を開発し有意なデータを研究の初期段階から取得することに成功した。また、ナノデバイスが発熱していない状態での特性を取得する方法も評価し、発熱時の特性と比較した。熱的特性の評価

では、コンピュータによる数値計算も活用した。本項目では、デバイスの構造と動作時温度の関係を明らかにし、熱散逸が良く温度上昇の少ないデバイス構造の実現を目指した。

- (2)ナノ半導体におけるフォノン特性の特異性の検証では、厚さ5nm以下という極薄膜のシリコンと厚さ3nm以下という極薄膜のシリコン酸化膜を有するMOS構造を作製し、非弾性トンネル分光法を活用した。非弾性トンネル分光法により、電子と強く相互作用し、電子を散乱するフォノンのエネルギーのシリコン膜厚依存性を調べることを目指した。

- (3)電界が高い場合のナノ半導体におけるキャリア輸送特性の基礎学理の確立では、極低温 (絶対温度で 2K 程度)において比較的エネルギーの高い電子を注入し、デバイス中の電子温度 を調べることで、電子ーフォノン相互作用のナノデバイス中での特異性を調べることを目指した。 また、4点曲げ装置を利用することで、外部応力がキャリア輸送特性に及ぼす影響を調べた。

- (4)熱・キャリア輸送の統合的理解によりナノ半導体を用いた高性能・超低消費電力の大規模 集積回路(グリーンチップ)を創製するための設計指針の構築では、実験データを解析することで デバイス・レベルでの動作温度低減指針を打ち出すことを目指した。また、コンピュータによる数 値計算(デバイスシミュレーション)を活用し、実際に作製することが困難な将来デバイスで、消費 エネルギーを低減するためのデバイス設計指針を打ち出すことを目指した。

#### 5. 研究成果 · 波及効果

目標とした4項目についての研究成果を以下に記載する。

- (1)ナノ半導体デバイスの熱的特性の評価

- ① ナノ温度計を用いたデバイス動作時の温度測定手法の開発

デバイス動作時の温度を測定する方法として、従来提案されていたゲート電極(ポリシリコン細線)の抵抗値の温度依存性を利用する方法を発展させた。ポリシリコン細線で高精度な温度評価を行うためには、空乏化とよばれる効果によるポリシリコン中の電子数変化を補正することが不可欠であることを示した(雑誌論文9)。また、ゲート電極材料として、ポリシリコンの代わりにニッケルとシリコンの化合物であるニッケルシリサイドを利用することで、従来では達成できなかったような高精度で温度を評価できることを示した。この成果は、デバイス分野で世界最高峰の学会である IEDM で発表し大変な注目を集めた(会議発表 2, 新聞・一般雑誌等掲載 1-4)。

② ナノデバイスの「無発熱」での特性を評価するための新手法の開発

ナノデバイスでは、熱の逃げ道が限られており、電流を流した瞬間にジュール発熱によってデバイスの温度が上昇してしまう(この効果を自己加熱とよぶ)。デバイス温度の上昇はデバイス特性の劣化を招く。しかし、作製したデバイスの特性が、この温度上昇によって劣化しているのか、その他の要因(寄生抵抗など)によって不十分なのかを区別することは極めて困難である。この区別を行うためには、デバイスの「無発熱時」の特性を評価することが不可欠になる。従来は、ACコンダクタンス法と呼ばれる方法が広く用いられていたが、我々は、この AC コンダクタンス法は決して「無発熱時」の特性を評価している訳ではないことを明確に示すとともに、無発熱時の特性を評価する新たな方法として修正パルス法を提案した。これらの成果を、デバイス分野で最高峰の国

際学会 IEDM で発表し大変な注目を集めた(会議発表 7)

## ③ ナノデバイスの温度特性を実験的に詳細に評価

①および②で開発した手法を駆使し、ナノデバイスの動作時の温度特性を詳細かつ高精度に評価した。その結果、従来は局所的な温度上昇が無視出来ると考えられていたバルク基板上に作製されたナノデバイスでも、有意な温度上昇が生じていることを世界で初めて明確に示した。また、薄い絶縁膜上に作製されたナノデバイスでは、やはり局所的な温度上昇はほとんど無いと考えられていたのに対し、温度上昇は確かに生じており、やはり無視できないことを示した。これらの成果は、ナノ半導体デバイスの熱的特性の評価という本課題の目標を高精度で達成したものである。国際学会 IEDM で発表し、産業界からも大変な関心をもって注目された(会議発表 2)。

④ 先端ナノデバイスの温度特性を数値計算により評価。また配線の影響を取り込む方法を開発世界的に広く使用されているデバイスシミュレータに独自の工夫を取り込むことで、先端の立体構造トランジスタの発熱特性をシミュレーションすることに成功した。その結果、バルク基板上に作製した立体構造トランジスタの方が、極薄膜酸化膜上に作製した立体構造トランジスタよりも動作時温度が上昇するという予想外の結果を世界に先駆けて示し、産業界・学界から非常に注目された(雑誌論文6、会議発表 9、22)。ナノデバイスでは配線による冷却効果も無視できないと考えられるが、銅などの従来材料だけでなく、カーボンナノチューブやグラフェンなどの新材料を配線に用いた場合の影響を、高速かつ高精度に評価可能な新手法を提案した(雑誌論文 2)。

### (2)ナノ半導体におけるフォノン特性の特異性の検証

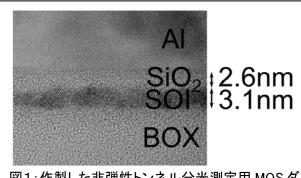

極薄膜シリコン(膜厚 5nm 以下)と極薄膜酸化膜(膜厚 3nm 以下)を有する MOS ダイオードを作製し(図1), 非弾性トンネル分光法により, ナノ半導体におけるフォノンのエネルギーを抽出した。その結果, 電子と強く相互し, 電子を散乱するフォノンでは, TA および LA モードのエネルギーは薄膜化に伴って小さくなることを発見し, フォノンの特異性

図1:作製した非弾性トンネル分光測定用 MOS ダイオードの断面透過電子顕微鏡写真

の検証という目標を達成した。従来、ナノデバイスでは量子効果で電子状態が変化することのみを考慮して(フォノンはバルク結晶と同じであるとして)デバイス特性の解析が行われていた。本成果は、このような従来の仮定(ナノデバイスでも電子とバルクフォノンの相互作用を考えることで良い)に変革を要請する学術的にも極めて重要なものである(具体的な成果発表は H26 年度の予定)。

#### (3) 電界が高い場合のナノ半導体におけるキャリア輸送特性の基礎学理の確立

ナノデバイスを実用化していくためには、電界が高い非平衡状態のキャリア輸送について十分に理解する必要がある。しかし、10nm以下のナノSiにおける熱輸送と非平衡キャリア輸送については、全く報告がなされていない。我々は、薄膜単結晶シリコンをチャネルとするトランジスタを

作製(シリコン膜厚 4nm~60nm)し、ナノ半導体中における非平衡キャリア輸送現象を調べた。その結果、Si/SiO<sub>2</sub>界面では、電子エネルギーから格子へのエネルギーの変換がより容易に行われることを実験的に世界に先駆けて示した(会議発表 8, 10, 13, 23)。ナノ半導体では体積に対する界面の比率が高くなるため、半導体/絶縁膜界面のこの特殊性は、ナノ半導体中におけるキャリア輸送の従来の考え方に大きな変革を迫るものである。これは、提案時には全く予想していなかった効果であり、当初の目標を超えた成果の一つといえる。ナノ半導体における歪みによる移動度変化は、このモデルにより実験データを高精度に再現可能である(雑誌論文 1)。

(4)キャリア輸送・熱輸送の統合理解により、ナノ半導体を用いた高性能・超低消費電力の大規模集積回路(グリーンチップ)を創製するための設計指針の構築

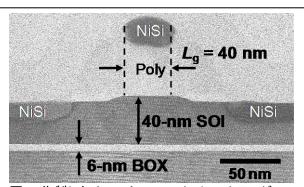

将来デバイス構造としては、絶縁膜上に作製されたトランジスタが有望である。(1)ー(3)までで得られた成果を活用し、実際に絶縁膜上にナノトランジスタ(図 2)を作製し、その熱特性を評価した。その結果、発熱を抑制するためには、(a)デバイス下部の絶縁膜を薄くする、(b)ソース/ドレイン領域の厚さを厚くする、(c)埋め込み絶縁膜下部の半導体へのドーピング濃度を下げる、(d)チャネルのドーピング濃度を

図2:作製したナノスケールのシリコントランジスタ。産総研ナノエレ研究部門との共同研究および TIA 推進本部の協力で作製。

下げる, これらの方針が有効であることを明らかにした(会議発表 2)。

また、熱に配慮したデバイス設計を行うことで低エネルギーLSIを実現可能であることを示すことに成功した。より具体的には、14nm世代のアナログ用トランジスタでは、熱配慮設計を行うことで、従来の素子構造に比べて、消費電力を1/3にまで低減できることを示した(具体的な成果発表はH26年度中の予定)。熱配慮設計は微細化が進むほどより有効になるため、将来のより微細なトランジスタでは消費エネルギーをより大幅に低減できると期待される。低エネルギー化のためのナノデバイスの熱配慮設計は、本課題で研究代表者が提唱している独自のものであり、その有効性が定量的に実証されたことの意義は大きい。

本課題で得られた成果は、半導体ー絶縁体界面における電子ーフォノン散乱の考え方に変革を迫るような学術的波及効果の大きいものから、ナノ半導体の熱配慮設計による低エネルギー化という産業的な波及効果の大きいものまで広範囲にわたる。ナノ半導体チャネルを用いた集積回路は、本提案後に量産化が開始された。本課題の成果は、今後市販されるナノ半導体集積回路の低エネルギー設計に生かされると予想され、またナノ半導体の学術的理解深耕をより推し進め、グリーン・イノベーションの推進に繋がると大いに期待できる。さらに研究代表者自身は、ナノ半導体における局所加熱(自己加熱)を利用した生体信号センサーの開発を開始しており、本課題の成果は提案当初に想定していた以上の波及効果を生む可能性を秘めている。

#### 6. 研究発表等

#### 雑誌論文

#### (掲載済みー査読有り) 計9件

計 11 件

- T. Ohashi, S. Oda, and K. Uchida, "Impact of Deformation Potential Increase at Si/SiO2 Interfaces on Stress-Induced Electron Mobility Enhancement in Metal?Oxide?Semiconductor Field-Effect Transistors," *Jpn. J. Appl. Phys.*, vol. 52, 04CC12 April, 2013. (6pages) doi:10.7567/JJAP.52.04CC12

- T. Takahashi, S. Oda, and K. Uchida, "Methodology for Evaluating Operation Temperatures of Fin-Type Field-Effect Transistors Connected by Interconnect Wires," *Jpn. J. Appl. Phys.*, vol. 52, 064203, May 2013. (7pages) doi:10.7567/JJAP.52.064203

- A. Shindome, T. Takahashi, S. Oda, and K. Uchida, "Experimental study on SET/RESET conditions for graphene resistive random access memory,", *Jpn. J. Appl. Phys.*, vol. 53, 04EN02, February 2014. (5 pages) doi:10.7567/JJAP.52.04CC03

- T. Ohashi, S. Oda, and K. Uchida, "Physical Mechanisms of Enhanced Uniaxial Stress Effect on Carrier Mobility in ETSOI MOSFETs," ECS Transactions, vol. 50, no. 9, 171-174, 2012.

- A. Shindome, Y. Doioka, N. Beppu, S. Oda, and K. Uchida, "Experimental Study of Two-Terminal Resistive Random Access Memory Realized in Mono- and Multilayer Exfoliated Graphene Nanoribbons," *Jpn. J. Appl. Phys.*, vol. 52, 04CN05, February 2013. (5 pages) doi:10.7567/JJAP.52.04CN05

- T. Takahashi, N. Beppu, K. Chen, S. Oda, and K. Uchida, "Self-Heating Effects and Analog Performance Optimization of Fin-Type Field-Effect Transistors," *Jpn. J. Appl. Phys.*, vol. 52, 04CC03, February 2013. (6 pages) doi:10.7567/JJAP.52.04CC03

- N. Kadotani, T. Takahashi, T. Ohashi, S. Oda, and K. Uchida, "Electron mobility enhancement in nanoscale silicon-on-insulator diffusion layers with high doping concentration of greater than 1E18 cm<sup>-3</sup> and silicon-on-insulator thickness of less than 10 nm," *J. Appl. Phys.*, vol. 110, no. 3, 034502 (7 pages), 2011. doi:10.1063/1.3606420

- N. Kadotani, T. Ohashi, T. Takahashi, S. Oda, and K. Uchida, "Experimental Study on Electron Mobility in Accumulation-Mode Silicon-on-Insulator Metal-Oxide-Semiconductor Field-Effect Transistors," *Jpn. J. Appl. Phys.*, vol. 50, 094101 (4 pages), September 2011. doi:10.1143/JJAP.50.094101

- N. Beppu, T. Takahashi, T. Ohashi, and K. Uchida, "Impact of Gate Poly Depletion on Evaluation of Channel Temperature in Silicon-on-Insulator Metal-Oxide-Semiconductor Field-Effect Transistors with Four-Point Gate Resistance Measurement Method," *Jpn. J. Appl. Phys.*, vol. 51, 02BC15 (5 pages), February 2012. doi:10.1143/JJAP.51.02BC15

#### (掲載済みー査読無し) 計1件

内田建,"シリコンナノ構造デバイスのキャリア輸送特性と熱配慮設計," 応用物理, vol. 83, no. 4, pp262-267, April, 2014.

## (未掲載) 計1件

M. Yamada, K. Uchida, and Y. Miyamoto, "Delay Time Component of InGaAs MOSFET Caused by Dynamic Source Resistance," *IEICE Trans. Elec.*, vol. E97-C, pp419-422, May 2014. (4 pages) doi:10.1587/transele.E97.C.419

### 会議発表 専門家向け 計59件

#### 計 59 件

- A. Shindome, T. Takahashi, S. Oda, and K. Uchida, "Experimental Study on SET/RESET Conditions for Graphene ReRAM," *International Conference on Solid State Devices and Materials* (SSDM), C-4-4, Fukuoka, Japan, Sep 25-27, 2013.

- T. Takahashi, T. Matsuki, T. Shinada, Y. Inoue, and K. Uchida, "Comparison of Self-Heating Effect (SHE) in Short-Channel Bulk and Ultra-Thin BOX SOI MOSFETs: Impacts of Doped Well, Ambient Temperature, and SOI/BOX Thicknesses on SHE," *Technical Digest of IEEE* International Electron Devices Meeting (IEDM), Washington D.C., USA, Dec 9-11, pp7.4.1-7.4.4, 2013.

- 3. K. Uchida, "Low Voltage -How Low Can We Go?", Technology Rump Session at 2013 Symposium on VLSI Technology, Kyoto, Japan, June 11, 2013. (Rump Session Moderator)

- K. Uchida, "How can we enhance LSI functionalities through Material/Device/Architecture Innovations?" Rump Session at 2013 *International Conference on Solid State Devices and Materials* (SSDM), Fukuoka, Japan, Sep 26, 2013. (Rump Session Moderator)

- K. Uchida, "Nanoscale Materials for LSI interconnects," *International Conference on Processing & Manufacturing of Advanced Materials* (THERMEC' 2013), Las Vegas, Dec 2-6, 2013. (Invited).

- 6. K. Uchida, "Extending the FETs," Short Couse at *IEEE International Electron Devices Meeting* (IEDM), Washington D.C., USA, Dec 8, 2013. (Short Course Lecture)

- N. Beppu, S. Oda, and K. Uchida, "Experimental Study of Self-Heating Effect (SHE) in SOI MOSFETs: Accurate Understanding of Temperatures during AC Conductance Measurement, Proposals of 2-omega Method and Modified Pulsed IV," *Technical Digest of IEEE International Electron Devices Meeting* (IEDM), San Francisco, CA, USA, Dec 8-10, pp641-644, 2012.

- 8. T. Ohashi, S. Oda, and K. Uchida, "Physical Mechanism of Enhanced Uniaxial Stress Effect on Carrier Mobility in ETSOI MOSFETs," 222nd ECS Meeting The SiGe, Ge, and Related Compounds Symposium, E17~E25-0155O, pp3118, Honolulu, HW, USA, October 7-12, 2012.

- T. Takahashi, N. Beppu, S. Oda, and K. Uchida, "Optimization of 14-nm Node Bulk/SOI FinFETs for SoC Platform: Thermal Conductivity, Operation Temperatures, and Analog Performance Analysis," *International Conference on Solid-Stated Devices and Materials* (SSDM), E-6-5L, pp823-824, September 25-27, 2012.

- T. Ohashi, T. Takahashi, T. Kodera, S. Oda, and K. Uchida, "Experimental Observation of Record-high Electron Mobility of Greater than 1100 cm2V-1s-1 in Unstressed Si MOSFETs and Its Physical Mechanisms," *International Conference on Solid-Stated Devices and Materials* (SSDM), E-5-1, pp807-808, September 25-27, 2012.

- A. Shindome, Y. Doioka, N. Beppu, S. Oda, and K. Uchida, "Graphene ReRAM towards All Graphene LSIs: Experimental Demonstration of Two-terminal ReRAM Operation in Electrically Broken Mono- and Multi-layer Graphene," *International Conference on Solid-Stated Devices and Materials* (SSDM), C-5-5L, pp690-691, September 25-27, 2012.

- N. Beppu, T. Takahashi, T. Ohashi, and K. Uchida, "Impact of Poly Depletion on Accurate Evaluation of Self-Heating Effects in SOI MOSFETs with Four-point Gate Resistance Measurement Method", *The Eighth International Nanotechnology Conference on Communication* and Cooperation, Tsukuba, Japan, May 8-11, 2012.

- 13. T. Ohashi, T. Takahashi, S. Oda and K. Uchida, "Experimental Evidence of Increased Deformation Potential at MOS Interface and Its Impact on Characteristics of ETSOI FETs," *The Eighth International Nanotechnology Conference on Communication and Cooperation*, Tsukuba, Japan, May 8-11, 2012.

- T. Takahashi, N. Beppu, K. Chen, S. Oda and K. Uchida, "Thermal-Aware Device Design of Nanoscale Bulk/SOI FinFETs," *The Eighth International Nanotechnology Conference on Communication and Cooperation*, Tsukuba, Japan, May 8-11, 2012.

- 15. K. Uchida, T. Takahashi, and N. Beppu, "Thermal-aware Device Design of Nano-scale FETs," *Tsukuba Nanotechnology Syposium* (TNS '12), p10, Tukuba, Japan, July 26, 2012 (Invited).

- K. Uchida, T. Takahashi, and N. Beppu, "Thermal-Aware Device Design of Nanoscale MOS Transistors," 2012 Asia-Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices (AWAD 2012), Naha, Japan, 8A-2, p288-289, June 29, 2012 (Invited).

- 17. K. Uchida and T. Ohashi, "Experimental Study on Deformation Potential at MOS Interface", *IEEE International Conference on Solid-State and Integrated Circuit Technology* (ICSICT), S13\_01, Xian, China, Oct. 29 Nov. 1, 2012 (Invited).

- T. Ohashi, S. Oda, and K. Uchida, "Impact of Deformation Potential Increase at Si/SiO2 Interfaces on Stress-Induced Electron Mobility Enhancement in MOSFET," *IEEE EDS WIMNACT* 37, P-15, Tokyo, Japan, February 18, 2013.

- K. Uchida and T. Takahashi, "Thermal-Aware Device Design of Nanoscale MOS Transistors," 16th International Workshop on Physics of Semiconductor Devices (IWPSD), MS-1-1, Kanpur, India, December 21, 2011 (Invited).

- 20. K. Uchida, "Carrier mobility in heavily-doped nanoscale SOI films," G-COE PICE International Symposium and IEEE EDS Minicolloquium on Advanced Hybrid Nano Devices: Prospects by World's Leading Scientists, Tokyo, Japan, October 5, 2011 (Invited).

- K. Uchida, N. Kadotani, T. Takahashi, "Carrier Transport in Ultrathin-body SOI FETs: Mobility in Channel and Diffusion Layers," IEEE 4th International Nanoelectronics Conference, Tao-Yuan, Taiwan, June 21-24, 2011 (Invited).

- 22. T. Takahashi, N. Beppu, K. Chen, S. Oda, and K. Uchida, "Thermal-Aware Device Design of Nanoscale Bulk/SOI FinFETs: Suppression of Operation Temperature and Its Variability," Technical Digest of IEEE International Electron Devices Meeting (IEDM), Washington D.C., WA, USA, pp809-812, Dec 5-7, 2011. doi:10.1109/IEDM.2011.6131672

- 23. T. Ohashi, T. Takahashi, N. Beppu, S. Oda, and K. Uchida, "Experimental Evidence of Increased Deformation Potential at MOS Interface and Its Impact on Characteristic of ETSOI FETs," Technical Digest of IEEE International Electron Devices Meeting (IEDM), Washington D.C., WA, USA, pp390-393, Dec 5-7, 2011. doi:10.1109/IEDM.2011.6131566

- T. Ohashi, T. Takahashi, S. Oda and K. Uchida, "Mechanism of Electron Mobility Enhancement in Junctionless SOI MOSFETs," G-COE PICE International Workshop, October 4-5, 2011

- 25. N. Beppu, T. Takahashi, T. Ohashi, and K. Uchida, G-COE PICE International Workshop, October 4-5, 2011.

- 26. N. Beppu, T. Takahashi, T. Ohashi, and K. Uchida, "Impact of Poly Depletion on Accurate Evaluation of Self-Heating Effects in SOI MOSFETs with Four-point Gate Resistance Measurement Method", International Conference on Solid-Stated Devices and Materials (SSDM), P-3-21L, pp124-125, September 28-30, 2011.

- 27. T. Takahashi, T. Kodera, S. Oda, and K. Uchida, "Experimental Study on Subband Structures and Hole Transport in (110) Si pMOSFETs under High Magnetic Field," The Seventh International Nanotechnology Conference on Communication and Cooperation, Albany, NY, USA, May 16-19, 2011.

- 28. 内田 建,「立体構造トランジスタ: 短チャネル効果・自己加熱・ばらつき」, STARC アドバンスト 講座(川崎市産業振興会館), 2013 年 5 月 14 日(依頼講演).

- 29. 内田 建, 「ナノスケール MOSFET のキャリア輸送」, 電子情報通信学会 2013 年ソサイエティ大会(福岡工業大学), C-12-26, 2013 年 9 月 18 日(受賞講演).

- 30. 高橋 綱己, 小田 俊理, 内田 建, 「熱特性モデル化による回路中の FinFET 動作温度評価手法」, 第74回応用物理学会秋季学術講演会(2013 秋 同志社大学)13.6 Si デバイス/集積化技術, 20a-C8-10, 2013 年9月16-20日(一般講演).

- 31. 新留 彩, 高橋 綱己, 小田 俊理, 内田 建, 「グラフェン抵抗変化型メモリの SET/RESET 条件に関する研究」, 第74回応用物理学会秋季学術講演会(2013 秋 同志社大学)17.3 新機能探索・基礎物性評価, 18a-B1-9, 2013 年9月16-20日(一般講演).

- 32. 黒澤裕也, 角谷尚哉, 高橋綱己, 大橋輝之, 小田俊理, 内田建, 「不純物のイオン化エネルギー増大によるナノワイヤトランジスタの電気的特性に与える影響」, 第 74 回応用物理学会秋季学術講演会(2013 秋 同志社大学)13.6 Si デバイス/集積化技術, 19p-C8-15, 2013 年 9 月 16-20 日. (一般講演)

- 33. 高橋綱己, 松木武雄, 品田賢宏, 井上靖朗, 内田建, 「ナノスケールバルクおよび極薄膜 BOX SOI MOSFET 動作温度の評価」, 電気学会 ナノエレクトロニクス集積化・応用技術調査専門委員会「原子層材料デバイスとナノスケール熱輸送」, 早稲田大学, 2014 年 3 月 14 日(依頼講演).

- 34. 内田 建,「ナノデバイスの熱配慮設計:高性能化と新機能創出」,第 61 回応用物理学関係講演会(2014 春 青山学院大学),13.半導体 A(シリコン)分科企画シンポジウム「ナノエレクトロニクスの新展開と国際連携」,17a-E1-3,2014年3月17日(招待講演).

- 35. 高橋綱己, 松木武雄, 品田賢宏, 井上靖朗, 内田建, 「4 端子ゲート抵抗法によるナノスケール バルク/極薄膜 BOX SOI MOSFET 動作温度の評価」,第 61 回応用物理学関係講演会(2014 春 青山学院大学), 13.4 半導体 A(シリコン) デバイス/集積化技術, 19a-F12-2, 2014 年 3 月 19 日(一般講演).

- 36. 高橋綱己, 別府伸耕, 陳君ろ, 小田俊理, 内田建, 「バルク/SOI FinFET の自己加熱およびアナログ特性の最適化」, 第 61 回応用物理学関係講演会(2014 春 青山学院大学), シリコンテクノロジー分科会論文賞および奨励賞記念講演, 19a-E4-5, 2014 年 3 月 19 日(受賞講演).

- 37. 新留彩, 高橋綱己, 小田俊理, 内田建, 「グラフェン抵抗変化型メモリの 3 端子動作に関する研究」, 第 61 回応用物理学関係講演会(2014 春 青山学院大学), 17.4 ナノカーボン デバイス 応用, 20a-E2-5, 2014 年 3 月 20 日(一般講演).

- 38. 高橋 綱己, 別府 伸耕, 小田 俊理, 内田 建, 「デバイスシミュレータを用いたナノスケール Bulk/SOI FinFET 熱等価回路モデルの導出」, 第 73 回応用物理学会学術講演会(2012 秋 愛媛大学・松山大学)13.6 Si デバイス/集積化技術, 13p-F4-2, 2012 年 9 月 11-14 日(一般講演).

- 39. 大橋 輝之,高橋 綱己,小寺 哲夫,小田 俊理,内田 建,「ユニバーサル曲線を超える MOSFET

- 移動度の観測とその物理的起源の解明」,第73回応用物理学会学術講演会(2012 秋 愛媛大学・松山大学)13.6 Si デバイス/集積化技術,13p-F4-12,2012 年9月11-14日(一般講演).

- 40. 新留 彩, 福田 祐樹, 小田 俊理, 内田 建, 「グラフェンナノリボン抵抗変化型メモリの実現」, 第73回応用物理学会学術講演会(2012 秋 愛媛大学・松山大学)17.3 新機能探索・基礎物性評価, 12p-C2-8, 2012 年9月11-14日(一般講演).

- 41. 内田 建, 大橋 輝之, 別府 伸耕, 高橋 綱己, 角谷 直哉, 「MOS 界面における変形ポテンシャルに関する実験的研究」, 第152回シリコンテクノロジー分科会研究集会「最先端シリコンナノエレクトロニクスの動向と今後の展開」, つくば, 2012 年9月4日(招待講演)

- 42. 高橋 綱己, 内田 建, 「FinFET 発熱解析によるアナログ特性最適化および素子温度モデル化」, 電気学会ナノエレクトロニクス集積化・応用技術調査専門委員会「ナノデバイスの熱管理工学」, 早稲田大学, 2012 年 11 月 30 日(招待講演)

- 43. 新留 彩, 土井岡 優, 別府 伸耕, 小田 俊理, 内田 建, 「単層および多層グラフェンナノリボン抵抗変化型メモリの実験的研究:動作メカニズムの解明へ向けて」, 応用物理学会 薄膜・表面物理分科会・シリコンテクノロジー分科会共催特別研究会「第 18 回ゲートスタック研究会」, 静岡, 2013 年 1 月 24-26 日(一般講演).

- 44. 内田建, 高橋綱己, 別府伸耕, 「熱に配慮した次世代集積回路のデバイス設計」, 日本学術振興会「先端ナノデバイス・材料テクノロジー第 151 委員会」平成24年度 第 4 回研究会「ナノスケールでの熱・エネルギーマネジメント技術」, 東京, 2013 年 2 月 4 日(招待講演).

- 45. 内田建, 高橋綱己, 別府伸耕, 「立体構造 SOI デバイスの自己加熱とデバイスの熱配慮設計」, 第157回シリコンテクノロジー分科会研究集会「SOI 関連技術の最近の進展」, 東京, 2013年2月22日(招待講演).

- 46. 内田建,「半導体技術ロードマップにおける新探求デバイス(Emerging Resaarch Device)とシリコンのナノサイエンス」、(独)産業技術総合研究所 電子光技術研究部門 第 2 回電子光技術シンポジウム、東京、2013 年 3 月 5 日(特別講演).

- 47. 大橋 輝之, 小田 俊理, 内田 建, 「歪みによる電子移動度向上へ MOS 界面における変形ポテンシャル上昇が与える影響」,第60回応用物理学会学術講演会(2013 春 神奈川工科大学)13.6 Si デバイス/集積化技術,28p-G9-17,2013 年3月27-30日(一般講演).

- 48. 新留 彩,別府 伸耕,高橋 綱己,小田 俊理,内田 建,「架橋・非架橋構造のグラフェン抵

- 抗変化型メモリの書込・消去特性」,第60回応用物理学会春季学術講演会(2013春 神奈川工科大学)17.3 新機能探索・基礎物性評価,29p-G10-3,2013年3月27-30日(一般講演).

- 49. 高橋 綱己, 別府 伸耕, 小田 俊理, 内田 建, 「熱配慮設計による FinFET アナログ特性の最適化」, 第60回応用物理学会春季学術講演会(2013 春 神奈川工科大学) 13.6 Si デバイス/ 集積化技術, 28p-G9-16, 2013 年 3 月 27-30 日(一般講演).

- 50. 高橋 綱己, 別府 伸耕, 陳 君璐, 小田 俊理, 内田 建, 「デバイスシミュレータを 用いたナノスケール Bulk/SOI FinFET の熱設計」,第 59 回応用物理学関係講演会 (2012 春 早稲田大学)13.6 Si デバイス/集積化技術, 17a-A1-9, 2012 年 15-18 日

- 51. 大橋 輝之, 高橋 綱己, 小田 俊理, 内田 建, 「MOS 界面における変形ポテンシャルの上昇」, 第 59 回応用物理学関係講演会(2012 春 早稲田大学)13.6 Si デバイス/ /集積化技術, 17a-A1-3, 2012 年 15-18 日.

- 52. 陳 君璐, 高橋 綱己, 別府 伸耕, 内田 健, 「High-k ゲートスタック構造における熱 伝導の比較」, 第 59 回応用物理学関係講演会(2012 春 早稲田大学)13.3 絶縁膜技術, 15p-GP1-5, 2012 年 15-18 日.

- 53. 新留 彩,福田 裕樹,小田 俊理,内田 建,「架橋多層グラフェンナノリボンにおける電荷数の温度依存性」,第 59 回応用物理学関係講演会(2012 春 早稲田大学) 17 ナノカーボン,15a-A3-31, 2012 年 15-18 日.

- 54. 別府 伸耕, 小田 俊理, 内田 建, 「AC コンダクタンス法及びパルス IV 法による自己 発熱抑制時の SOI MOSFET ドレイン電流評価」, 第 59 回応用物理学関係講演会 (2012 春 早稲田大学) 13.6 Si デバイス/集積化技術, 17a-A1-8, 2012 年 15-18 日.

- 55. 内田 建, 「STRJ Extended CMOS コンセプト」, 第 72 回応用物理学会学術講演会 (2011 秋 山形大学)シンポジウム "Extended CMOS のための Deterministic ドーピング, 単一ドーパントデバイス", 2011 年 8 月 29 日 9 月 2 日.

- 56. 内田 建,「ナノ半導体のデバイス応用:トランジスタ応用を中心として」,第 72 回応用 物理学会学術講演会(2011 秋 山形大学)チュートリアル,2011 年 8 月 29 日 9 月 2 日

- 57. 陳 君璐, 高橋 綱己, 別府 伸耕, 内田 健, 「High-k ゲートスタック構造における熱 伝導に関する研究」, 第 72 回応用物理学会学術講演会(2011 秋 山形大学)13.1 基礎物性・評価, 1p-J-11, 2011 年 8 月 29 日 - 9 月 2 日.

- 58. 大橋 輝之, 高橋 綱己, 小寺 哲夫, 小田 俊理, 内田 建, 「低温・強磁場環境 を利用した極薄膜 SOI 中の変形ポテンシャルの評価」, 第72回応用物理学会学術講演会(2011 秋 山形大学)13.1 基礎物性・評価, 2a-J-11, 2011 年8月29日-9月2日.

- 59. 別府伸耕, 高橋綱己, 大橋輝之, 陳 君璐, 内田 建, 「SOI MOSFET における自己 加熱の実験的評価:電子熱伝導は寄与するか?」, 第72 回応用物理学会学術講演

|              | <b>△</b> (2014 和 山東土光) 40.0 0 元 (1 / - / / 年 川 十/ / -                            |

|--------------|----------------------------------------------------------------------------------|

|              | 会(2011 秋 山形大学), 13.6 Si デバイス/集積化技術, 1a-P7-11, 2011 年 8 月 29                      |

|              | 日一9月2日.                                                                          |

|              | 一般向け計の件                                                                          |

| 図書           |                                                                                  |

|              |                                                                                  |

| 計0件          |                                                                                  |

| 産業財産         | (取得済み)計0件                                                                        |

| 権<br> 出 願・取  | (出願中)計0件                                                                         |

| 得状況          |                                                                                  |

| 計0件          |                                                                                  |

| Webペー        | 1. 慶應義塾大学 内田研究室                                                                  |

| ジ            | www.ssn.elec.keio.ac.jp                                                          |

| (URL)        | 2. Youtube 慶大 内田研究室 http://www.youtube.com/watch?v=wO_eDt4Gqg0                   |

|              | 3. プレスリリース「ナノメートル・スケールトランジスタ動作中温度の正確な測定に成功~次世代                                   |

|              | 半導体集積回路の長期間安定動作へ道~」                                                              |

|              | http://www.keio.ac.jp/ja/press_release/2013/kr7a4300000csww4.html                |

|              | http://www.aist.go.jp/aist_j/press_release/pr2013/pr20131209_2/pr20131209_2.html |

|              |                                                                                  |

| 国民との         | 1. 平成 25 年度慶應義塾大学 理工学部 オープンキャンパス                                                 |

| 科学・技<br>術対話の | 表題:「スマホのデータ処理をつかさどる電子デバイスの最先端/未来技術」                                              |

| 実施状況         | 実施日: 平成 25 年 8 月 21 日 9:30~16:00                                                 |

|              | 場所: 慶應義塾大学 矢上キャンパス                                                               |

|              | 対象者: 一般(主として高校生)                                                                 |

|              | 参加者数: 約 1800 名(オープンキャンパス全体)                                                      |

|              | 内容: 身近なスマートフォンに使われている半導体技術の紹介にはじまり、今後スマートフ                                       |

|              | オンをより高性能化していくためには、ナノ素子の活用とその特性の電気的・熱的観点からの                                       |

|              | 最適化が必要であることを説明。質疑応答形式で参加者との対話も行った。                                               |

|              | 2. 平成 25 年度慶應義塾大学 理工学部 矢上祭                                                       |

|              | 表題: 「ナノスケール半導体を用いた電子デバイスの研究」                                                     |

|              | 実施日: 平成 25 年 10 月 12 日, 13 日                                                     |

|              | 対象者: 一般(主として大学生および高校生)                                                           |

|              | 参加者数: 約 10000 名(矢上祭全体)                                                           |

|              | 内容: 身近なスマートフォンに使われている半導体技術の紹介にはじまり、今後スマートフ                                       |

|              | オンをより高性能化していくためには、ナノ素子の活用とその特性の電気的・熱的観点からの                                       |

|              | 最適化が必要であることを、ポスター展示を中心に説明した。質疑応答形式で参加者との対                                        |

|              | 話も行った。                                                                           |

|              | BH O11 ン/こ。                                                                      |

3. 平成 25 年度慶應テクノモール

表題: 「ナノスケール熱管理工学による新デバイスの創造と機能向上」

実施日: 平成 25 年 12 月 13 日 10 時~18 時

場所: 東京国際フォーラム 地下 2階 展示ホール 2

対象者: 一般

参加者数: 約1000名

内容: ナノスケールの電子デバイスは、ナノスケールの小さな空間に電流を流すことと微細化による熱伝導率の劣化により、自己加熱とよばれる発熱現象の影響を強く受けていることを説明。我々は、この自己加熱によって生じた熱をマネージメントすることで、既存デバイスの性能を良くしたり、新機能デバイスを創出することを目指している研究活動について説明。質疑応答形式で参加者との対話も行った。また、ラウンドテーブルセッション II 「新機能性マテリアルから育つ夢」で登壇し、ナノデバイスの将来像と熱マネージメントの重要性について講演を行った。

4. 平成 24 年度慶應テクノモール

表題: 「ナノスケール熱工学によるグリーンLSI」

実施日: 平成 24 年 12 月 7 日 10 時~18 時

場所: 東京国際フォーラム 地下2階 展示ホール

対象者: 一般

参加者数: 約 1000 名

内容: ナノスケールの電子デバイスを集積化したLSIは、大きな電流をナノスケールの小さな空間に流すため、自己加熱とよばれる発熱現象の影響を強く受けている。我々は、この自己加熱によって生じた熱を、積極的に生かしたり、あるいはうまく逃がしたりすることで、地球環境に優しいグリーンなLSIの実現を目指していることを説明した。

5. 東工大が誇る若手研究者

表題: 「半導体とナノテクノロジー:ナノスケールの電気抵抗」

実施日: 平成 23 年 10 月 29 日

場所: 東京工業大学 大岡山キャンパス 西2号館4階1号室

対象者: 高校生・一般

参加者数: 58名

内容: 携帯電話やパソコンの高性能化は、半導体電子デバイスを小さくすることで実現されてきた。導体の長さを短くすると電気抵抗が小さくなるように、電子デバイスを小さくし電気抵抗を抑えることで、半導体集積回路のスピードを向上してきたのである。対話講演会では、このようなオームの法則が成り立たないほど小さくなった近年の電子デバイスを、高性能かつ低消費電力化するための最先端の戦略について紹介した。

# 様式21

| 新聞·一       | 1. | マイナビニュース(2013 年 12 月 11 日) 「IEDM2013- 慶應大など, ナノスケールトランジスタの    |

|------------|----|---------------------------------------------------------------|

| 般雑誌等<br>掲載 |    | 精密な温度測定に成功」 <u>http://news.mynavi.jp/news/2013/12/10/066/</u> |

| 計3件        | 2. | 化学工業日報(2013 年 12 月 12 日) 「微細トランジスタ 動作中温度を正確測定 慶大/産総           |

|            |    | 研」                                                            |

|            | 3. | 日刊工業新聞(2013年 12月 27日)「ナノ素子 動作温度 正確に測定 慶大 回路の信頼性               |

|            |    | 向上へ」                                                          |

| その他        |    |                                                               |

|            |    |                                                               |

|            |    |                                                               |

# 7. その他特記事項

# •授賞

エレクトロニクスソサイエティ賞, 内田建,「ナノスケール MOSFET のキャリア輸送に関する先駆的研究」, 電子情報通信学会, 平成 25 年 9 月